# Upgrade of the PreProcessor System for the ATLAS LVL1 Calorimeter Trigger: from ASICs to FPGA

Andrei Khomich Kirchhoff-Institut für Physik, Universität Heidelberg

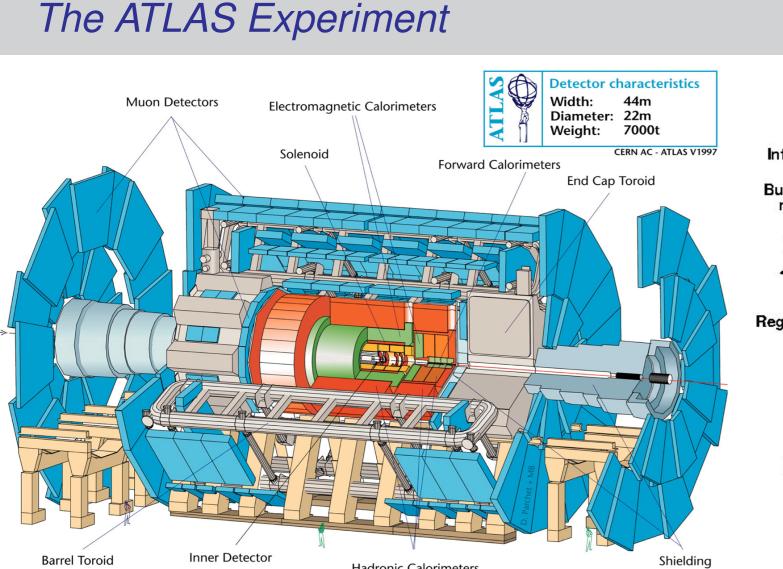

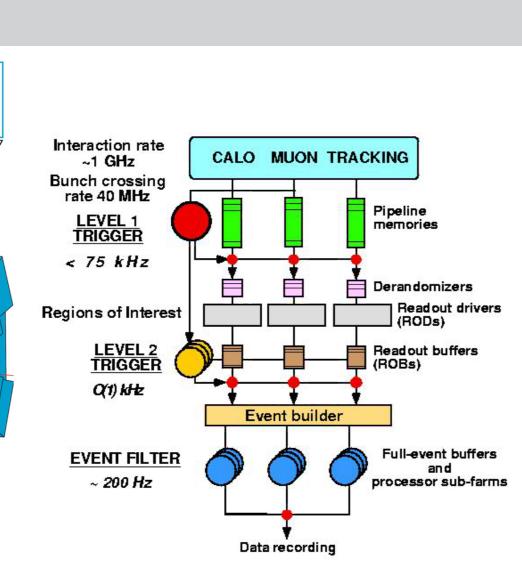

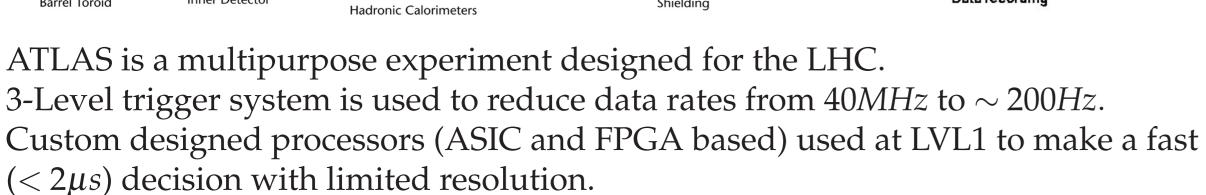

Based on Trigger Towers i.e. presummed Calorimeter signals

- Two step system:

- Preprocessing: Digitisation and Bunch Crossing Identification

- Processing: Search for electron, jet and tau candidates, determination of *MissingE<sub>T</sub>* and *SumE<sub>T</sub>*

*Features of the Real-time Data Path:* Fixed Latency ( $\sim 1 \mu s$ ); Pipeline processing; Massive parallelism;

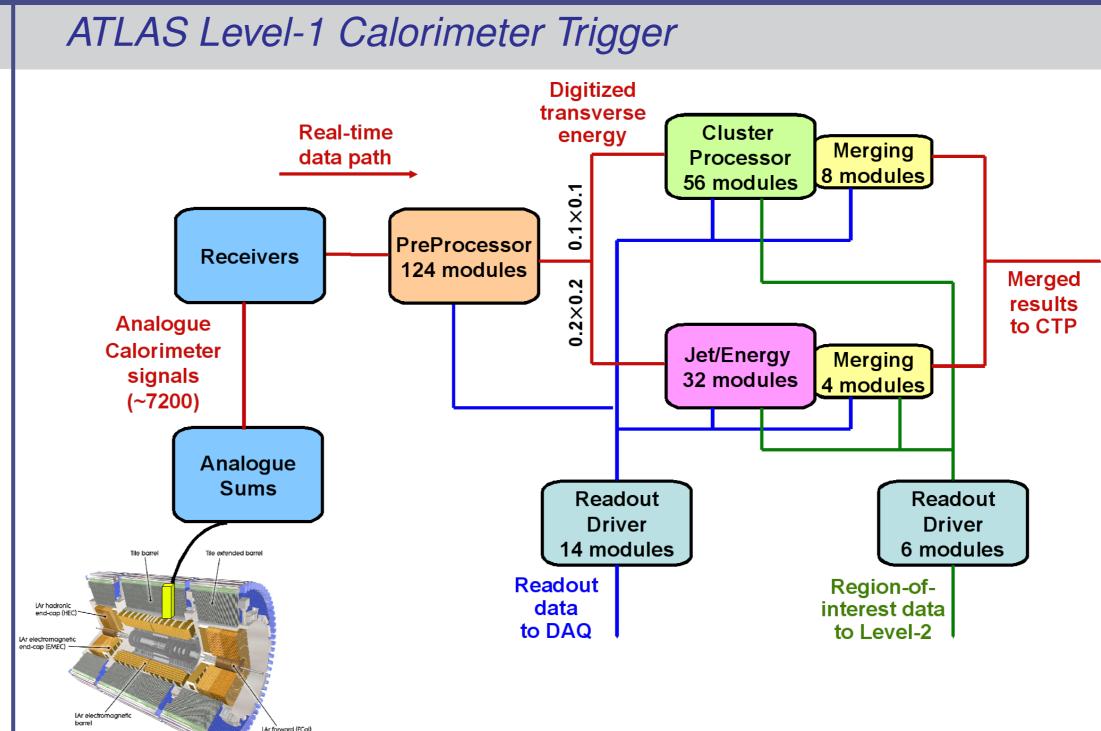

#### The PreProcessor System: 124 PreProcessor Modules

#### New MCM. Motivation.

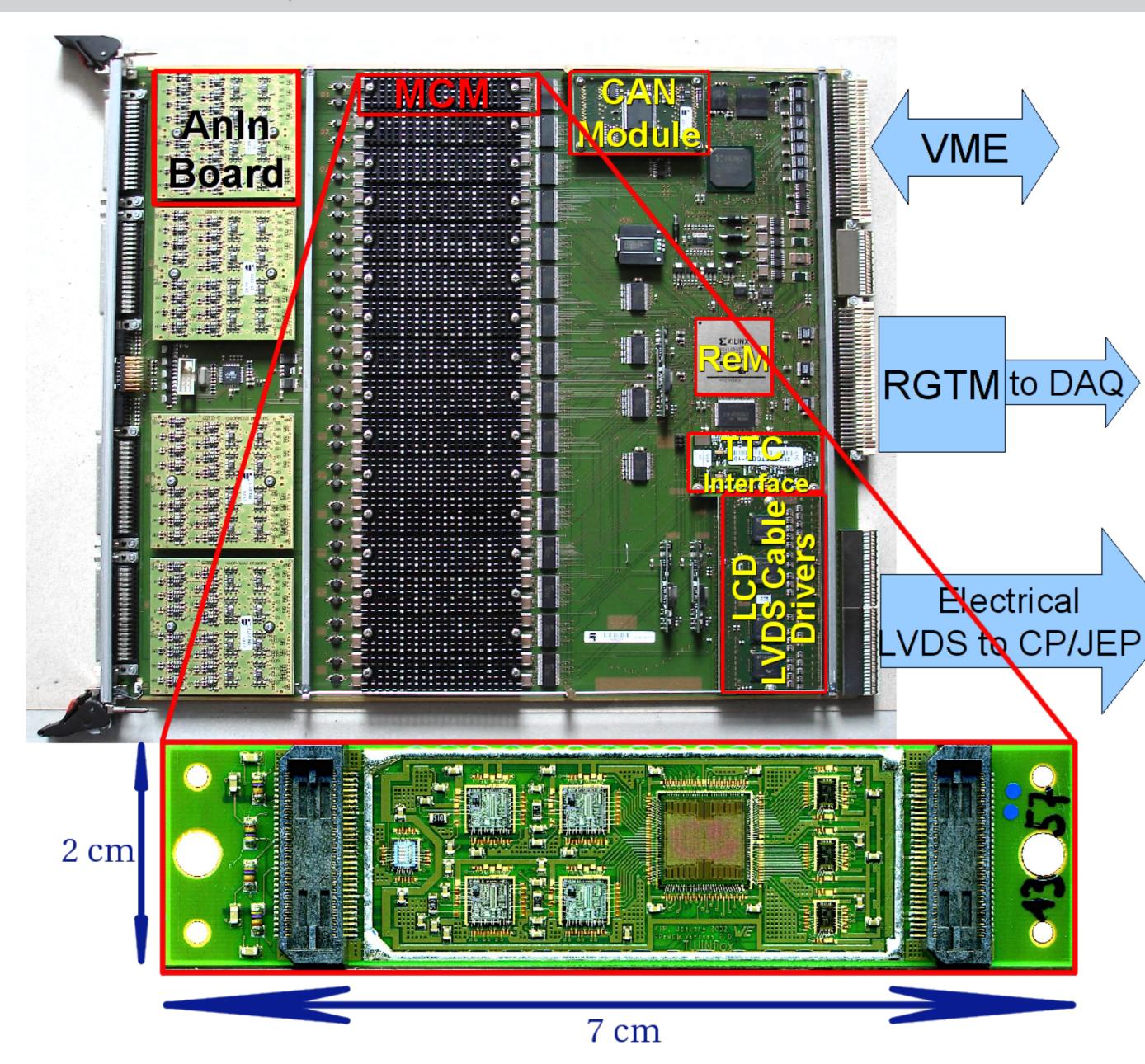

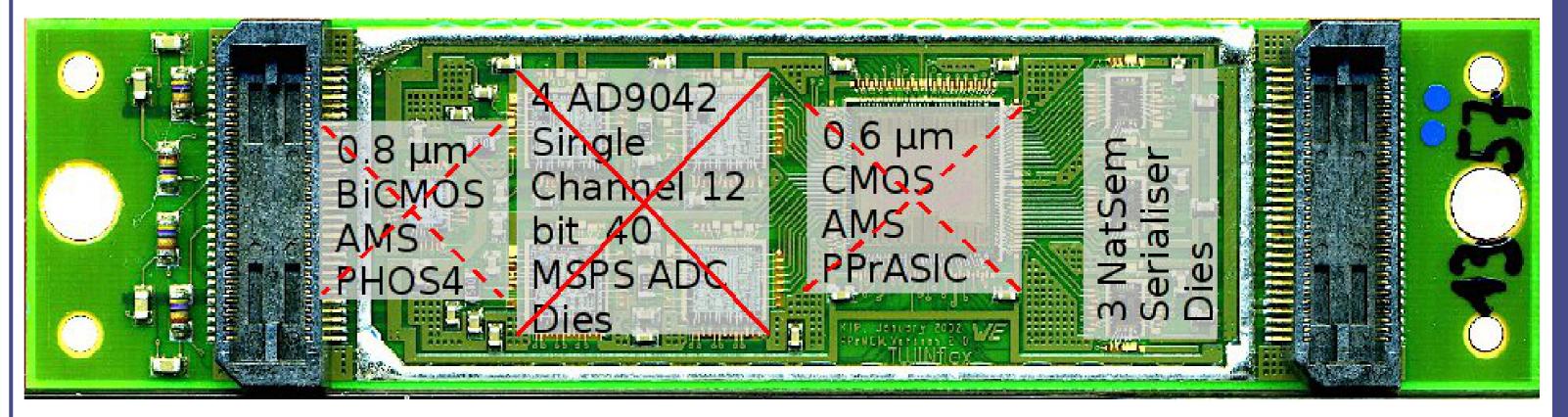

VERY conservative spare policy(50%) has been implemented, but we would not be able to produce quickly more MCMs

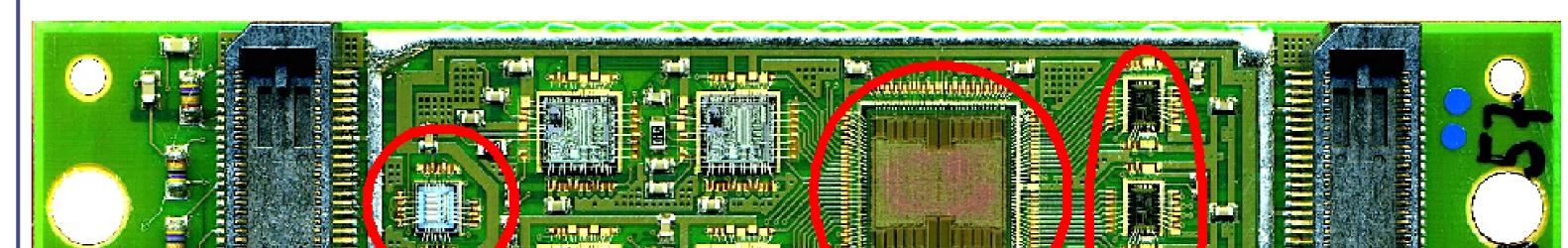

9 ASIC Dies on each of 2048 MCMs in the System

- PHOS4 (time-adjustment chip with 1ns resolution): GDSII available, process (still) available, success uncertain, no support

- AD9042: n/a as unpackaged die anymore, packaged version has prohibitive size

- **PPrASIC**: Verilog available, process (still) available, GDSII available, outdated technology (0.6μ*m*)

- **Serialisers**: available, new pin compatible DS92LV1023E is recommended by NatSem

### New MCM

- Processing is performed on a Multi Chip Module (MCM):

- ► 10(12)-bit, 40 MHz, 3 BC delay, 595 mW per channel digitisation

- 1 ns sampling time adjustment

- BCID (2 methods)

- Look-up table based calibration

- Histogramming, playback

- Jet-summing

- ► 400(480) Mbit/s serialisation

- ► 13 BC ticks from analog in to Jet (summed) serial output

# AD9218 Spartan

#### Test 1. PHOS4 replacement: FPGA for time-adjustment

## AD9218

- We would like to develop a pin-, size- and latency-compatible substitute for the MCM based on todays components.

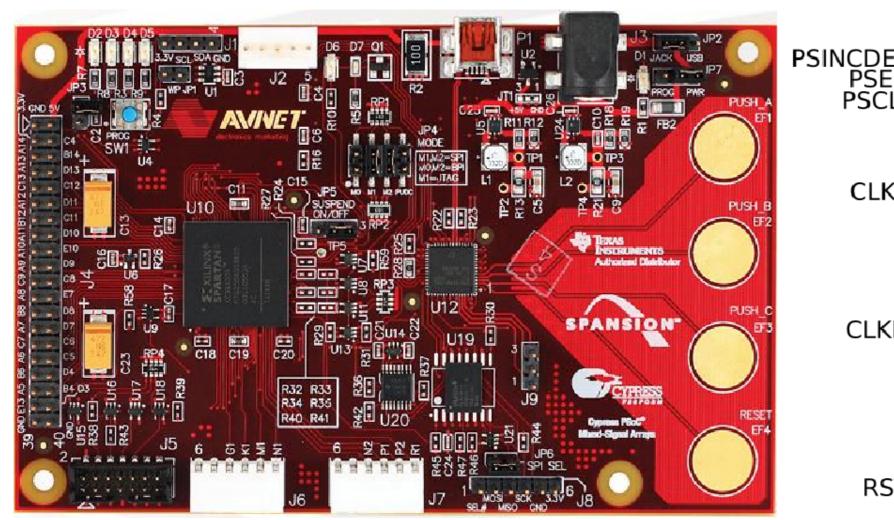

- Candidates for the main parts are two AD9218 (dual 105 MHz FADC) and a Spartan-3A(or Spartan-6)

- Spartan-6 currently has limited availability

- Spartan-3A (for ex. XC3S1400A) can be used for design and tests now

- ► Minimum components on board: 2 ADCs and FPGA is it possible?

### Test 2. LVDS serialisers in FPGA

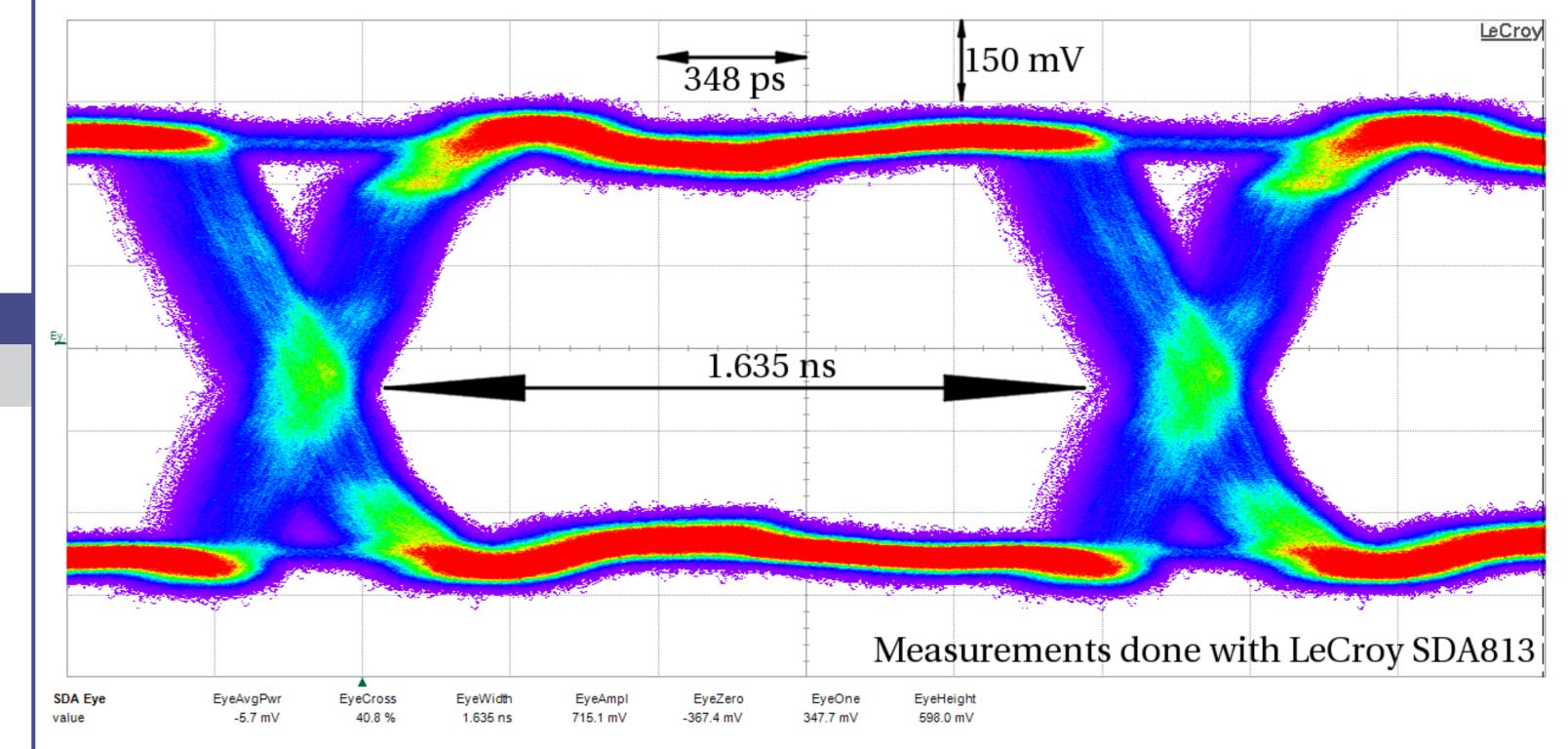

#### **480 Mbits/s**: (10 data bits + 1 start bit + 1 stop bit) @ 40MHz

Eye-diagram shows a good signal quality confirming that even XC3S400A can be used as a serialiser:

- AVNET development board with XC3S400A-4FTG256C Spartan-3A FPGA in the suitable for MCM package is used for testing

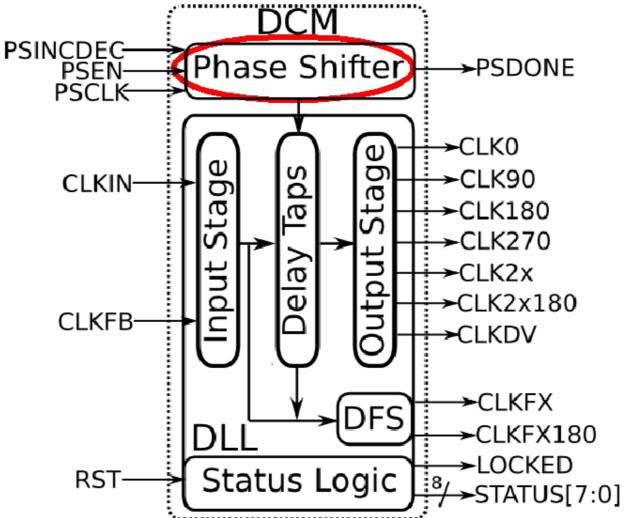

- PHOS4 chip task is fine time adjustment (resolution: 1 ns). This job can be done by FPGA's Digital Clock Manager (DCM):

- Phase Shifter step is well bellow 1 ns

- ► There are 8 DCMs in the XC3S1400A and 4 of them can be used for PHOS4 replacement (4 channels)

#### Conclusions

- ► New MCM (nMCM) can be built with the same form-factor and functionality

- ► Having a reconfigurable component (FPGA) we will gain in flexibility

- ► PHOS4 functionality and LVDS serialisers can be implemented inside FPGA ⇒ less components on the module

- First tests shows that even Spartan-3A can be used

- Various FPGA evaluation boards, together with existing equipment for current MCM testing is used for development and tests before actual layout of the nMCM will be ready.

Implemented using DDR I/O. 3 serialisers occupy <2% of the XC3S400A + 1 DCM